لماذا نصاب بالجنون نحن عشاق الهاتف في كل مرة ينتقل فيها المسبك إلى عقدة معالجة جديدة؟ الاستجابة الأساسية التي يمكنني التفكير فيها هي أنه مع انخفاض عقدة العملية، ينخفض أيضًا حجم الترانزستورات المستخدمة في الشريحة. تعني الترانزستورات الأصغر حجمًا أنه يمكن وضع عدد أكبر منها داخل الشريحة مما يزيد من عدد الترانزستورات، وكلما زاد عدد الترانزستورات، أصبحت الشريحة أكثر قوة و/أو كفاءة في استخدام الطاقة.

ومن الأمثلة الجيدة التي نستخدمها كثيرًا هو iPhone. في عام 2019، تم تشغيل خط iPhone 11 بواسطة شريحة A13 Bionic مقاس 7 نانومتر والتي تحتوي على 8.5 مليار ترانزستور. في عام 2020، تم تجهيز خط iPhone 12 بمعالج 5nm A14 Bionic الذي يحمل 11.8 مليار ترانزستور. وأعقب ذلك في العام التالي باستخدام شريحة A15 Bionic بدقة تصنيع 5 نانومتر لتشغيل طرازات iPhone 13. حملت تلك الشريحة 15 مليار ترانزستور. تتميز سلسلة iPhone 14 Pro بمعالج A16 Bionic بدقة تصنيع 4 نانومتر والذي يحتوي على 16 مليار ترانزستور. يعد iPhone 15 Pro وiPhone 15 Pro Max حاليًا الهواتف الذكية الوحيدة التي تستخدم شريحة 3 نانومتر، A17 Pro، التي تحتوي على عدد ترانزستور يبلغ 19 مليار.

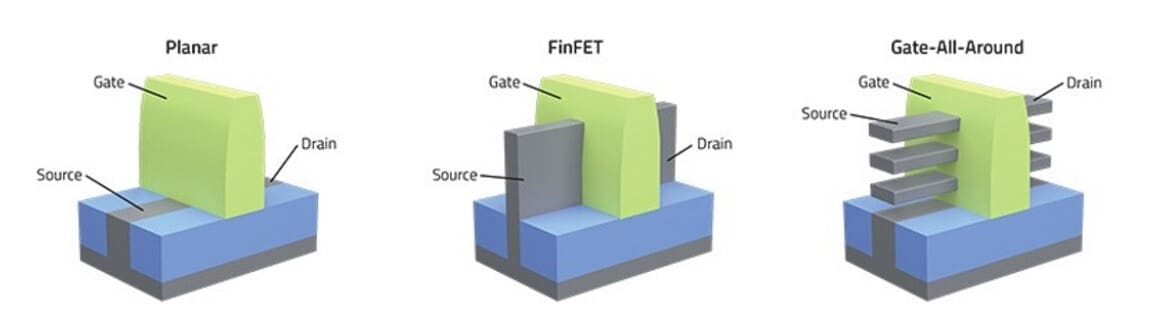

بحلول عام 2025، ستستخدم شركات Intel وSamsung Foundry وTSMC جميعها ترانزستورات البوابة الشاملة

ستبدأ Samsung Foundry أيضًا في إنتاج شرائح 2 نانومتر بكميات كبيرة في عام 2025، ووفقًا لشركة Tom's Hardware، في عام 2027، من المتوقع أن تنتقل إلى عقدة معالجة 1.4 نانومتر. عند 1.4 نانومتر، من المتوقع أن تضيف سامسونج ورقة نانوية رابعة والتي ستزيد من تيار محرك الأقراص وتحسن أداء الشريحة من خلال السماح بتدفق المزيد من التيار عبر كل ترانزستور. تم تقليل التسرب الحالي من خلال جعل الرقائق المنتجة بدقة 1.4 نانومتر أكثر كفاءة في استخدام الطاقة. مع زيادة التحكم في تدفق التيار، فإن الترانزستورات المصنعة عند 1.4 نانومتر سوف تولد حرارة أقل مما يزيد من كفاءة الطاقة.

كما أشرنا، فإن شركة Samsung بدأت التفوق على TSMC باستخدام GAA الآن مع عقدة المعالجة 3nm الخاصة بها. وبينما لن تنضم TSMC إلى النادي حتى تصل إلى 2 نانومتر في عام 2025، فإن Intel ستتفوق عليها في عام 2024 بعقدة المعالجة 20A الخاصة بها والتي ستستخدم أيضًا GAA (والتي تسميها RibbonFET). بحلول الوقت الذي تبدأ فيه كل من Intel وTSMC في استخدام GAA، سيكون لدى Samsung خبرة في ذلك.

ستستخدم جميع المسابك الثلاثة أيضًا توصيل الطاقة الخلفي بسرعة 2 نانومتر (20 أمبير لشركة Intel التي تطلق على نسختها Power Via). يؤدي هذا إلى نقل كافة توصيلات الطاقة من أعلى الشريحة إلى أسفلها مما يتيح مساحة أكبر لوصلات البيانات الموجودة فوق السيليكون ويساعد في إنشاء اتصالات طاقة أكبر في الجزء السفلي من الشريحة. سيؤدي هذا أيضًا إلى تحسين أداء الشريحة.