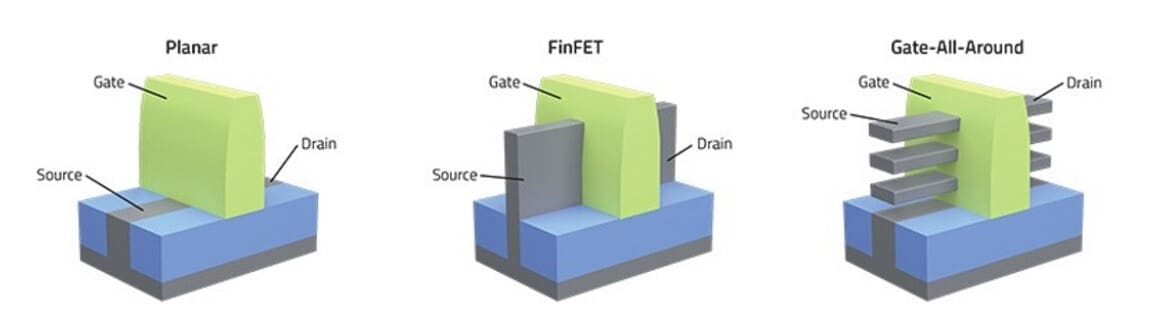

Pourquoi sommes-nous, les passionnés de téléphone, devenons fous à chaque fois qu'une fonderie passe à un nouveau nœud de processus ? La réponse la plus élémentaire à laquelle je puisse penser est que, à mesure que le nœud de processus diminue, la taille des transistors utilisés dans une puce diminue également. Des transistors plus petits signifient qu'un plus grand nombre d'entre eux peuvent tenir à l'intérieur d'une puce, ce qui augmente le nombre de transistors et plus le nombre de transistors est élevé, plus une puce est puissante et/ou économe en énergie.

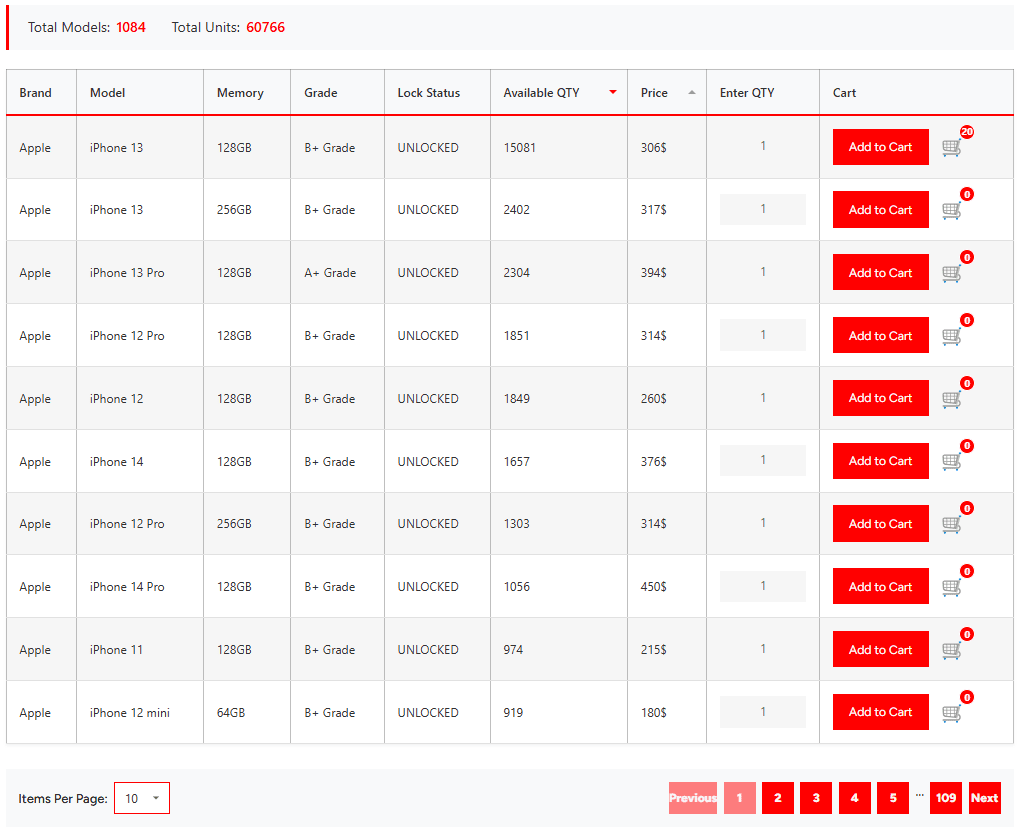

Un bon exemple que nous utilisons souvent est l’iPhone. En 2019, la gamme iPhone 11 était alimentée par le A13 Bionic 7 nm qui contenait 8,5 milliards de transistors. En 2020, la gamme iPhone 12 était équipée du A14 Bionic 5 nm qui transportait 11,8 milliards de transistors. Cela a été suivi l’année suivante avec le 5 nm A15 Bionic utilisé pour alimenter les modèles d’iPhone 13. Cette puce transportait 15 milliards de transistors. La série iPhone 14 Pro comportait le A16 Bionic 4 nm qui contenait 16 milliards de transistors. L'iPhone 15 Pro et l'iPhone 15 Pro Max sont actuellement les seuls smartphones à utiliser une puce de 3 nm, l'A17 Pro, qui possède un nombre de transistors de 19 milliards.

D’ici 2025, Intel, Samsung Foundry et TSMC utiliseront tous des transistors Gate-All-Around

Samsung Foundry commencera également à produire en masse des puces de 2 nm en 2025 et, selon Tom's Hardware, en 2027, elle devrait passer au nœud de processus de 1,4 nm. À 1,4 nm, Samsung devrait ajouter une quatrième nanofeuille qui augmentera le courant de commande et améliorera les performances d'une puce en permettant à davantage de courant de circuler à travers chaque transistor. Les fuites de courant sont encore réduites, ce qui rend les puces produites à 1,4 nm encore plus économes en énergie. Avec le contrôle accru du flux de courant, les transistors fabriqués à 1,4 nm généreront moins de chaleur, augmentant ainsi l'efficacité énergétique.

Comme nous l'avons souligné, Samsung prend une longueur d'avance sur TSMC en utilisant désormais GAA avec son nœud de processus 3 nm. Et même si TSMC ne rejoindra pas le club avant d'atteindre 2 nm en 2025, Intel le battra en 2024 avec son nœud de processus 20A qui utilisera également GAA (qu'il appelle RibbonFET). Au moment où Intel et TSMC commenceront à utiliser GAA, Samsung en aura l'expérience.

Les trois fonderies utiliseront également une alimentation électrique arrière à 2 nm (20 A pour Intel qui appelle sa version Power Via). Cela déplace toutes les connexions d'alimentation du haut de la puce vers le bas, ce qui laisse plus de place aux interconnexions de données au-dessus du silicium et contribue à créer des connexions d'alimentation plus grandes au bas de la puce. Cela entraînera également une amélioration des performances de la puce.